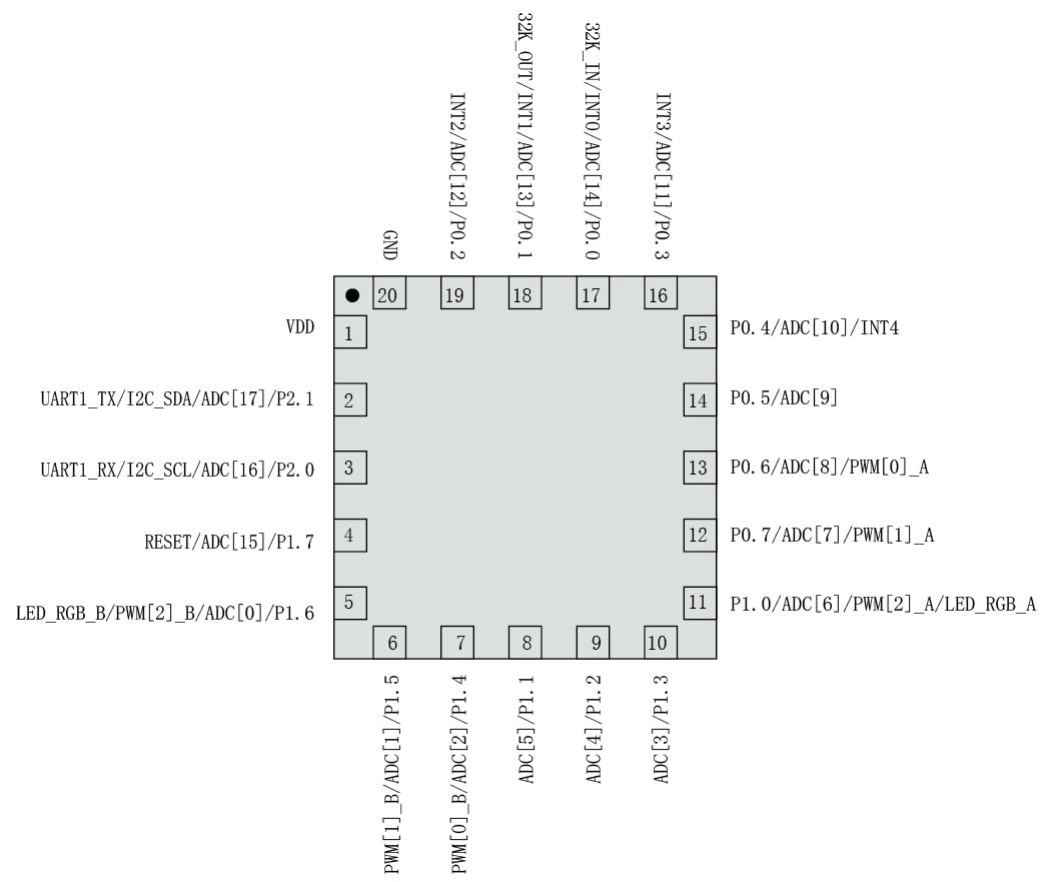

CA51M020N2

The CA51M020N2 chip is an 8-bit microcontroller based on the 1T 8051 core, which not only retains the basic characteristics of traditional 8051 chips, but also runs 10 times faster than traditional 8051 chips in general, with superior performance. The chip is equipped with 4KB MTP program memory, 256Byte internal RAM, 256Byte external RAM, and 512Byte EEPROM. It also integrates functional modules such as 18 channels of 12 Bit ADC, 3 channels of 16 Bit PWM, 1 channel of hardware LED0RGB cascade control, 1 channel of I2C, 1 channel of UART, and low voltage detection (LVD). Supports three power-saving modes: IDLE, STOP, and low-speed operation to adapt to applications with different power consumption requirements. Its powerful functions and superior anti-interference performance make it widely applicable to various household appliances and consumer products.

Product Details

Kernel

CPU: 1T 8051, higher speed 10 times faster than traditional 8051

Compatible with 8051 instruction set, dual DPTR working mode

Memory

MTP program memory: 4KB, with more than 1000 repeated erasures

EEPROM: 512 Byte, used to store data that needs to be saved after power failure, with more than 100000 repeated erasures

RAM: 256 Bytes internal RAM, 256 Bytes external RAM

Working voltage

Working voltage: 2.7V~ 5.5V@Fosc =8MHz 2.2V~ 5.5V@Fosc =4MHz

Working temperature

Working temperature: -40 ℃~+85 ℃

Clock system

External low-speed oscillator: 32.768KHz

Built in low-speed RC oscillator: 128KHz

Built in high-speed RC oscillator: 8MHz, accuracy of ± 2% @ 5V/25 ℃ (factory calibrated)

Timer

Two 16 bit universal timers: Timer 0, Timer 1

Universal Input/Output Port (GPIO)

Supports up to 18 GPIO ports

Supports push-pull, open drain, pull-up (30K), pull-down (30K), and high resistance modes

When outputting by push-pull, there are four levels of push current options for GPIO: 10mA, 8mA, 6mA, and 5mA@ VDD=5V

When pushing and pulling output, there are two levels of GPIO current available: 16mA and 8mA@ VDD=5V

GPIO can be software simulated as a 1/2 BIAS LCD driver without the need for external resistors

TMC function

The clock source of TMC timer can be selected as IRCL or XOSCL

The minimum unit of interruption time is 512 IRCL clock cycles when the clock source is selected as IRCL, and 128 XOSCL clock cycles when the clock source is selected as XOSCL

The configurable interrupt time is 1-256 minimum unit times

Interrupt system

7 valid interrupt sources

Two level interrupt priority, supporting nested interrupts

5 external interrupt sources INT0~INT4. External interrupt triggering edge selection: INT0~1 (rising edge, falling edge), INT2~4 (rising edge, falling edge, double edge)

Interrupt input pin selection: INT0 (P0.0), INT1 (P0.1), INT2 (P0.2), INT3 (P0.3), INT4 (P0.4): Analog to Digital Converter (ADC)

Supports 18 channel 12 bit SAR ADCs

Supports two reference voltage sources: VDD and internal reference

Selecting internal voltage as the reference can measure VDD voltage

PWM

Supports 3 PWM outputs, each path can be individually controlled, and the cycle and duty cycle can be freely configured within a 16 bit range

Supports direct output of internal clock function and PWM interrupt function

Supports PWM output pin mapping: PWM0 (P1.4/P0.6), PWM1 (P1.5/P0.7), PWM2 (P1.6/P1.0)

Supports 1 hardware cascade module with a scanning frequency of 800Kbps/S, directly controlling WS2812 or similar driver chips, meeting the requirements of monochrome or seven color LED strip products

Universal Serial Interface (UART1)

Supports 1 full duplex serial port

Supports 1-byte receive cache

I2C interface

Built in 1-channel I2C interface, supporting master-slave mode, standard/fast/high-speed mode

Low Voltage Detection (LVD)

The detection voltage can be set to 2.7V, 3.3V, 3.7V, 4.2V

Low voltage reset or interrupt can be set

Reset mode

The chip supports multiple reset sources: power on/power off reset, soft reset, hard reset, watchdog reset, low voltage detection reset

Watchdog

27 bit watchdog timer, 16 bit adjustment accuracy, configurable watchdog reset or interrupt

Program download and simulation

Support ISP method for downloading programs

Support online simulation function

Low power consumption

STOP mode, current<7uA

IDLE mode, current<33uA

Package type: QFN20